https://hdlbits.01xz.net/wiki/Problem_sets

Problem sets - HDLBits

hdlbits.01xz.net

※ begin/end문

begin 내에 있는 코드는 순서대로 실행된다

※ Blocking vs Non-Blocking

Blocking

'=' 을 통해서 할당함, SW코드 처럼 순차적으로 실행됨, Combinational Logic

ex)

원래 a==0 일 때

a = 1;

b = a;

따라서 a와 b 모두 1이 존재

Non-Blocking

'<=' 을 통해서 할당함, 윗줄의 코드가 끝나기 전에 동시에 실행 따라서 병렬처리, Sequential Logic

ex)

원래 a==0 일 때

a <= 1;

b <= a;

a==1 이고 b==0

Alwaysblock1

Combinational의 경우 assign과 aways @(*)을 통해서 구현 가능

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always @(*)

begin

out_alwaysblock = a & b;

end

endmodule

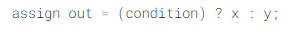

※ conditional operator

※ if

※ case

Always_if

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = (sel_b1 & sel_b2 == 1) ? b : a;

always @(*)

begin

if (sel_b1 & sel_b2 == 1)

out_always = b;

else

out_always = a;

end

endmodule

Always_case

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'd0 : out = data0;

3'd1 : out = data1;

3'd2 : out = data2;

3'd3 : out = data3;

3'd4 : out = data4;

3'd5 : out = data5;

default : out = 4'd0;

endcase

end

endmodule

※ Priority Encoder

https://www.electronics-tutorials.ws/combination/comb_4.html

Priority Encoder and Digital Encoder Tutorial

Electronics Tutorial about the Priority Encoder and Positional Digital Encoder used to generate Binary Codes in Combinational Logic Circuits

www.electronics-tutorials.ws

module top_module (

input [3:0] in,

output reg [1:0] pos );

always @(*) begin

casex(in)

4'b0001 : pos = 2'b00;

4'b001x : pos = 2'b01;

4'b01xx : pos = 2'b10;

4'b1xxx : pos = 2'b11;

default : pos = 2'bxx;

endcase

end

endmodule

Always_nolatches

// synthesis verilog_input_version verilog_2001

module top_module (

input [15:0] scancode,

output reg left,

output reg down,

output reg right,

output reg up );

always @(*) begin

{left, down, right, up} = 4'b0000;

case (scancode)

16'he06b : left = 1'b1;

16'he072 : down = 1'b1;

16'he074 : right = 1'b1;

16'he075 : up = 1'b1;

endcase

end

endmodule

'전자공학 > 디지털회로' 카테고리의 다른 글

| [Verilog] Basic Gate (0) | 2022.12.20 |

|---|---|

| [Verilog] More Verilog Features (0) | 2022.12.20 |

| [Verilog] Module (0) | 2022.12.14 |

| [Verilog] Vector (0) | 2022.12.13 |

| [Verilog] Flip-Flop (0) | 2022.12.13 |

댓글