https://hdlbits.01xz.net/wiki/Problem_sets

Problem sets - HDLBits

hdlbits.01xz.net

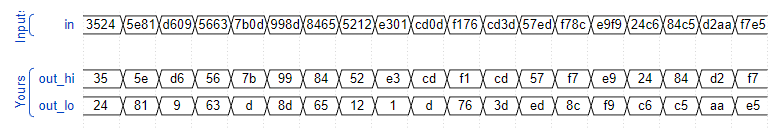

Vector1

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

Vector2

module top_module(

input [31:0] in,

output [31:0] out );

assign out = {in[7:0], in[15:8], in[23:16], in[31:24]};

endmodule

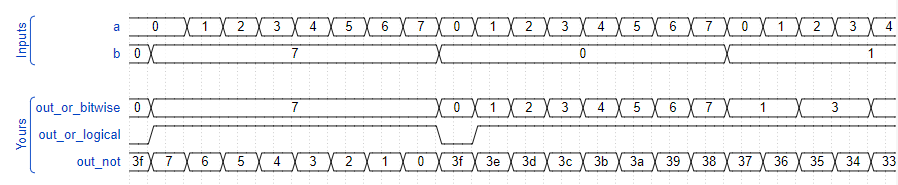

Vectorgates

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a|b;

assign out_or_logical = a||b;

assign out_not = {~b,~a};

endmodule

Vectorr

벡터를 역으로

※ assign out[7:0] = in[0:7]; 는 작동하지 않음

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0], in[1], in[2], in[3], in[4], in[5], in[6], in[7]};

endmodule

Vector4

부호(MSB)를 유지하면서 벡터를 확장

module top_module (

input [7:0] in,

output [31:0] out );

assign out = {{24{in[7]}}, in};

endmodule

'전자공학 > 디지털회로' 카테고리의 다른 글

| [Verilog] Procedures (0) | 2022.12.15 |

|---|---|

| [Verilog] Module (0) | 2022.12.14 |

| [Verilog] Flip-Flop (0) | 2022.12.13 |

| [Verilog] 기본 gate (0) | 2022.12.12 |

| VLSI 요약 (0) | 2022.12.08 |

댓글