https://hdlbits.01xz.net/wiki/Problem_sets

Problem sets - HDLBits

hdlbits.01xz.net

Hadd

Half Adder(반가산기)

module top_module(

input a, b,

output cout, sum );

assign cout = a & b;

assign sum = a ^ b;

endmodule

Fadd

Full Adder(전가산기)

module top_module(

input a, b, cin,

output cout, sum );

assign cout = a&b | b&cin | cin&a;

assign sum = a ^ b ^ cin;

endmodule

※ Half Adder vs Full Adder

carry_in이 있으면 Full 없으면 Half

ece241_2014_q1c

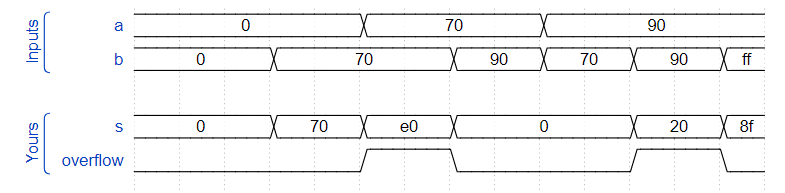

overflow를 감지하는 회로 설계

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

);

assign s = a + b;

// always @(*) begin

// overflow = 0;

// if(a[7] == b[7])

// if(a[7] != s[7])

// overflow = 1;

// end

assign overflow = ~a[7]&~b[7]&s[7] | a[7]&b[7]&~s[7];

endmodule※ overflow가 발생하기 위해서는 2값의 최상위 비트가 같을 때 두값의 합의 최상의 비트가 다르면 발생

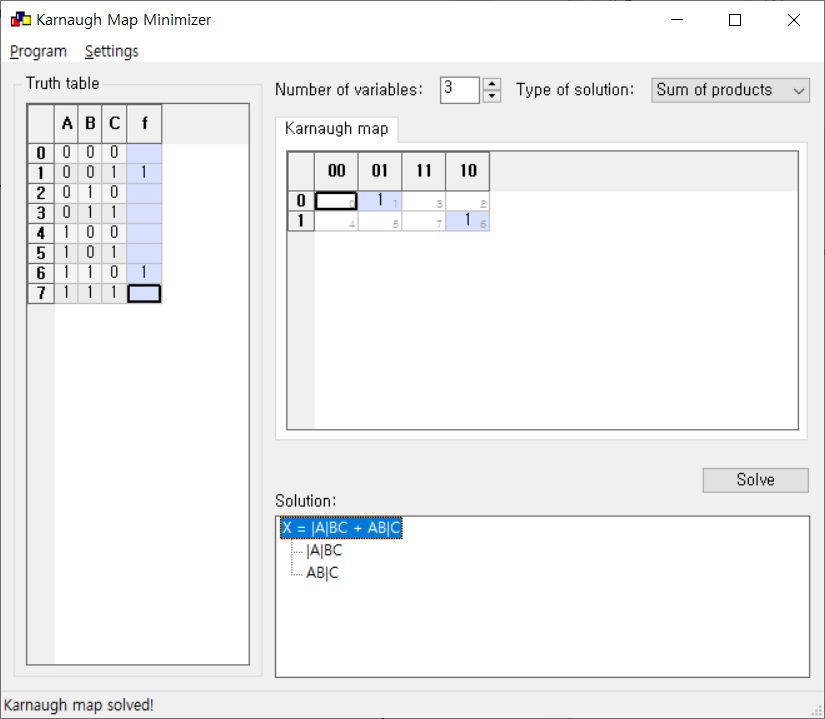

※ 진리표를 이용해서 간소화

'전자공학 > 디지털회로' 카테고리의 다른 글

| [Verilog] Gate-Level에서 D Latch & D Flip-Flop (0) | 2022.12.25 |

|---|---|

| [Verilog] Latches and Flip-floops (0) | 2022.12.22 |

| [Verilog] Multiplexer (1) | 2022.12.21 |

| [Verilog] Basic Gate (0) | 2022.12.20 |

| [Verilog] More Verilog Features (0) | 2022.12.20 |

댓글