분주(Prescaler)

클럭을 줄이는 것

카운터를 이용해서 설계함 아래 필기에 설명

`timescale 1ns/1ps

module pre1000(

input i_clk ,

input n_rst ,

output reg o_clk

);

reg [8:0] counter500;

always @(negedge n_rst, posedge i_clk) begin

if(!n_rst) begin

counter500 <= 0;

o_clk <= 0;

end

else if(counter500<499) begin

counter500 <= counter500 + 1;

end

else begin

counter500 <= 0;

o_clk = ~o_clk;

end

end

endmodule

pre1000.v

0.00MB

tb_pre1000.v

0.00MB

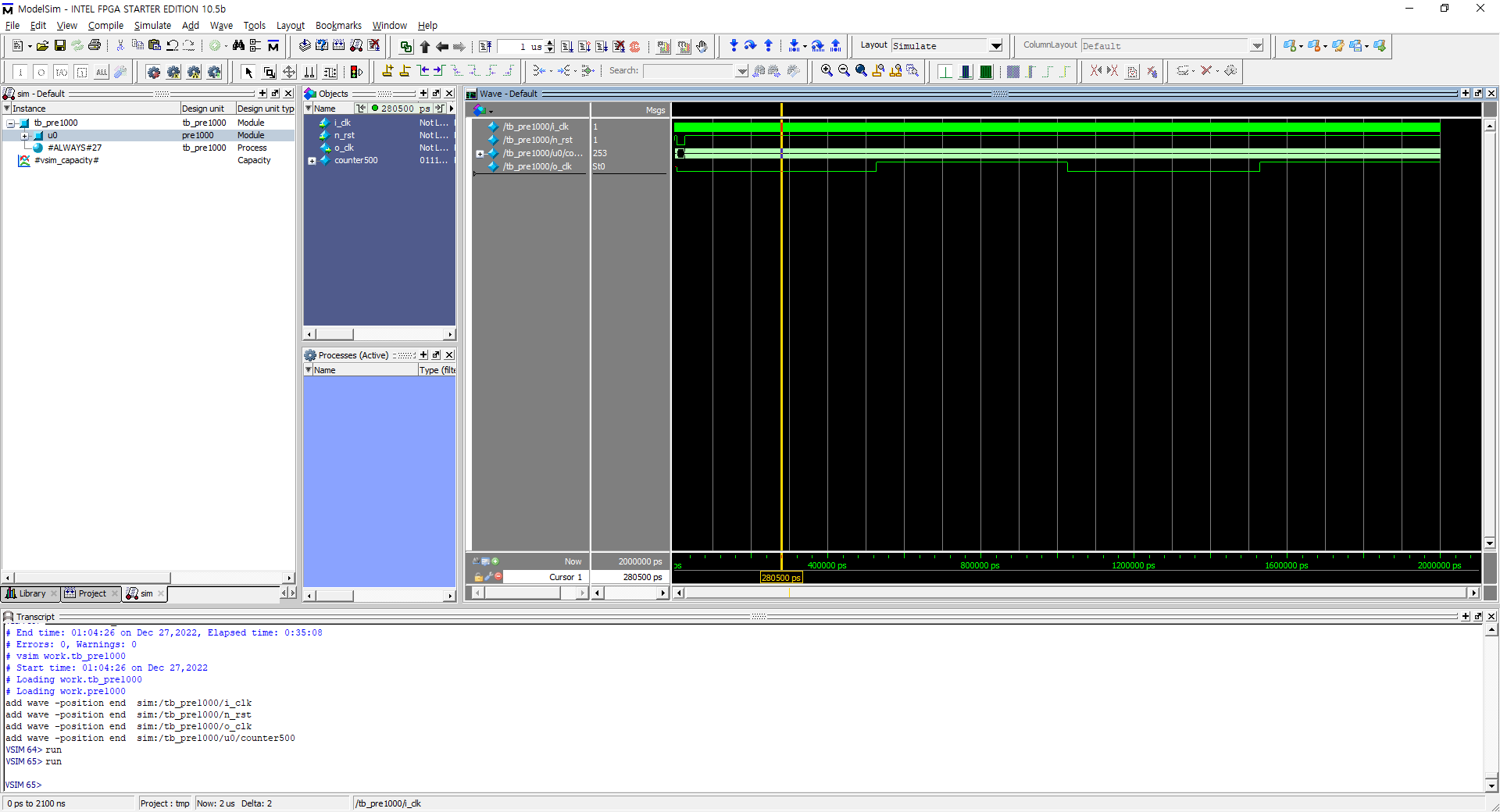

리셋이 끝난후 카운팅이 시작됨

#0.5 clk = ~clk이므로 1주기에 1000ps(=1ns)이다.

527500ps에서 rising edge

1027500ps에서 falling edge

1527500ps에서 rising edge

따라서 1주기에 1000000ps (=1000*1000ps =1us)이다.

'전자공학 > 디지털회로' 카테고리의 다른 글

| [Verilog] 125MHz -> 1KHz 분주기 (0) | 2022.12.29 |

|---|---|

| [Verilog] Counter (0) | 2022.12.26 |

| [Verilog] Gate-Level에서 D Latch & D Flip-Flop (0) | 2022.12.25 |

| [Verilog] Latches and Flip-floops (0) | 2022.12.22 |

| [Verilog] Arithmetic Circuit (0) | 2022.12.21 |

댓글